Tiêu chuẩn ngành TCN68-172:1998 về giao diện kết nối mạng – Yêu cầu kỹ thuật do Tổng cục Bưu điện ban hành đã được thay thế bởi Quy chuẩn kỹ thuật Quốc gia QCVN 02:2010/BTTTT về đặc tính điện/vật lý của các giao diện điện phân cấp số do Bộ trưởng Bộ Thông tin và Truyền thông ban hành .

Nội dung toàn văn Tiêu chuẩn ngành TCN68-172:1998 về giao diện kết nối mạng – Yêu cầu kỹ thuật do Tổng cục Bưu điện ban hành

TCN 68 – 172: 1998

GIAO DIỆN KẾT NỐI MẠNG

YÊU CẦU KỸ THUẬT

INTERFACES FOR INTERCONNECTION

TECHNICAL REQUIREMENT

MỤC LỤC

Lời nói đầu

1. Phạm vi áp dụng

2. Thuật ngữ và khái niệm

3. Các yêu cầu kỹ thuật

Tài liệu tham khảo

LỜI NÓI ĐẦU

Tiêu chuẩn TCN 68 – 172: 1998 được xây dựng trên cơ sở các khuyến nghị của Liên minh Viễn thông quốc tế.

TCN 68 – 172: 1998 do Viện Khoa học kỹ thuật Bưu điện biên soạn, Vụ Khoa học công nghệ – Hợp tác quốc tế đề nghị và được Tổng cục Bưu điện ban hành theo Quyết định số 610/1998/QĐ-TCBĐ ngày 29 tháng 9 năm 1998.

GIAO DIỆN KẾT NỐI MẠNG

YÊU CẦU KỸ THUẬT

INTERFACES FOR INTERCONNECTION

TECHNICAL REQUIREMENT

(Ban hành theo Quyết định số 610/1998/QĐ-TCBĐ ngày 29 tháng 9 năm 1998 của Tổng cục trưởng Tổng cục Bưu điện)

1. Phạm vi áp dụng

1.1 Tiêu chuẩn này quy định các yêu cầu kỹ thuật đối với các giao diện tín hiệu số tốc độ 2048 kbit/s và giao diện tín hiệu đồng bộ 2048 kHz.

1.2 Tiêu chuẩn này là cơ sở kỹ thuật cho việc kết nối mạng của các doanh nghiệp cung cấp dịch vụ viễn thông.

2. Thuật ngữ và khái niệm

Tiêu chuẩn này áp dụng thuật ngữ và khái niệm sau đây:

Luật mã hóa HDB3 được xác định như sau: Mỗi khối 4 bit 0 liền nhau được thay thế bằng 000V tương ứng hoặc B00V. Việc lựa chọn giữa 000V hay B00V được thực hiện sao cho số các xung B giữa hai xung V liên tiếp là lẻ. Nói cách khác, chuỗi xung V liên tiếp là có cực tính xen kẽ để không tạo ra thành phần một chiều.

Lưu ý: Các chữ viết tắt có nghĩa như sau:

HDB3 – High Density Bipolar of order 3-mã lưỡng cực mật độ cao bậc 3

3. Các yêu cầu kỹ thuật

3.1 Yêu cầu kỹ thuật đối với giao diện 2048 kbit/s

3.1.1 Đặc tính chung

Tốc độ: 2048 kbit/s ± 50 ppm.

Mã: mã lưỡng cực mật độ cao bậc 3 (HDB3).

Yêu cầu về bảo vệ quá áp được quy định trong mục 3.3

3.1.2 Chỉ tiêu kỹ thuật tại cổng ra

Các yêu cầu kỹ thuật đối với cổng ra tín hiệu 2048 kbit/s được quy định tại bảng 1.

Bảng 1: Các chỉ tiêu kỹ thuật tại cổng ra giao diện 2048 kbit/s

3.1.3 Chỉ tiêu kỹ thuật tại cổng vào

|

Dạng xung (Dạng danh định là hình chữ nhật) |

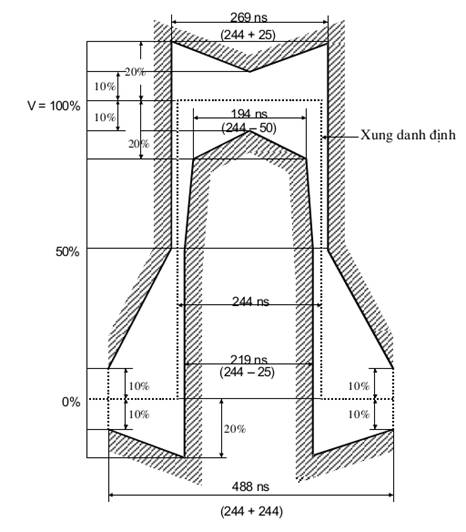

Tất cả các xung của tín hiệu hợp lệ phải tuân theo mặt nạ xung như quy định trong hình 1 (đối với mọi cực tính). Giá trị V tương ứng với giá trị đỉnh danh định. |

|

|

Đôi dây cho mỗi hướng |

Đôi cáp đồng trục |

Đôi dây đối xứng |

|

Trở kháng tải thử, W |

Điện trở thuần 75 |

Điện trở thuần 120 |

|

Điện áp đỉnh danh định khi có xung, V |

2,37 |

3 |

|

Điện áp đỉnh danh định khi không có xung, V |

0 ± 0,237 |

0 ± 0,3 |

|

Độ rộng xung danh định, ns |

244 |

|

|

Tỷ số biên độ giữa xung dương và xung âm tại điểm giữa của khoảng xung |

0,95 ¸ 1,05 |

|

|

Tỷ số độ rộng giữa xung dương và xung âm tại điểm có biên độ bằng nửa biên độ danh định |

0,95 ¸ 1,05 |

|

|

Giá trị rung pha đỉnh – đỉnh cực đại tại cổng ra |

Tuân theo mục 3.3.1 của Tiêu chuẩn TCN 68-164:1997 |

|

3.1.3 Chỉ tiêu kỹ thuật tại cổng vào

Tín hiệu số tại cổng vào được xác định như tại mục 3.1.2 của tiêu chuẩn này nhưng được phép thay đổi bởi đặc tính của đôi dây kết nối. Suy hao của đôi dây này phải tuân theo luật Öf, và suy hao tại tần số 1024 kHz phải nằm trong dải từ 0 đến 6 dB. Suy hao này có tính đến bất kỳ sự suy giảm nào xảy ra do sự có mặt của giá phân bố tín hiệu số giữa các thiết bị.

Rung pha cổng vào phải tuân theo các quy định tại mục 3.3.3.2 của Tiêu chuẩn TCN 68-164: 1997.

3.1.4 Suy hao phản xạ tại cổng vào phải không nhỏ hơn giá trị tối thiểu được quy định tại bảng 2.

Ghi chú: V tương ứng với giá trị đỉnh danh định

Hình 1: Mặt nạ xung tại giao diện 2048 kbit/s

Bảng 2: Giá trị suy hao phản xạ tối thiểu tại cổng vào

|

Dải tần số (kHz) |

Suy hao phản xạ (dB) |

|

51 ¸ 102 102 ¸ 2048 2048 ¸ 3072 |

12 18 14 |

3.1.5 Để không bị ảnh hưởng của hiện tượng phản xạ tín hiệu xảy ra do sự không đồng nhất về trở kháng tại các giá phân bố tín hiệu số và tại các cổng ra số, các cổng vào phải thỏa mãn yêu cầu sau:

Tín hiệu tổng danh định được mã hoá theo mã HDB3 và có dạng xung như được xác định trong mặt nạ xung, phải thêm vào các tín hiệu này tín hiệu nhiễu có dạng xung giống như dạng xung của tín hiệu mong muốn. Tín hiệu nhiễu phải có tốc độ nằm trong giới hạn như quy định ở tiêu chuẩn này, nhưng không được đồng bộ với tín hiệu mong muốn. Tín hiệu nhiễu phải được kết hợp với tín hiệu mong muốn trong mạng kết hợp với tổng suy hao của luồng tín hiệu là 0 và trở kháng danh định là 120 W (trong trường hợp giao diện đôi dây đối xứng) và 75 W (trong trường hợp giao diện cáp đồng trục) để đạt được tỷ số tín hiệu/nhiễu là 20 dB. Cấu trúc nhị phân của tín hiệu nhiễu phải tuân theo khuyến nghị O.151 (chu kỳ 215-1 bit). Khi luồng tín hiệu bị suy hao với giá trị bằng giá trị suy hao cực đại cho phép của cáp kết nối ở cổng vào cũng không được phép có lỗi.

3.1.6 Tiếp đất lớp dẫn điện bên ngoài và lớp vỏ bọc

Lớp dẫn diện bên ngoài của cáp đồng trục và vỏ bọc của đôi dây đối xứng phải được nối đất tại cổng ra. Trong trường hợp cần thiết thì vỏ bọc này phải được nối đất tại cả cổng vào.

3.2 Yêu cầu kỹ thuật đối với giao diện đồng bộ 2048 kHz

3.2.1 Đặc tính chung

Giao diện này áp dụng trong các trường hợp việc đồng bộ được thực hiện bởi tín hiệu đồng bộ ngoài 2048 kHz.

Yêu cầu về bảo vệ quá áp được quy định trong mục 3.3.

3.2.2 Chỉ tiêu kỹ thuật tại cổng ra.

Các chỉ tiêu kỹ thuật tại cổng ra được quy định tại bảng 3.

3.2.3 Chỉ tiêu kỹ thuật tại cổng vào

Tín hiệu tại cổng vào được xác định như trên nhưng được thay đổi bởi đặc tính của đôi dây kết nối.

Bảng 3: Các chỉ tiêu kỹ thuật tại cổng ra giao diện đồng bộ 2048 kHz

|

Tần số |

2048 kHz ± 50 ppm |

|

|

Dạng xung (Dạng danh định là hình chữ nhật) |

Tín hiệu phải tuân theo mặt nạ như quy định trong hình 2. Giá trị V tương ứng với đỉnh cực đại của xung |

|

|

Đôi dây cho mỗi hướng |

Cáp đồng trục |

Đôi dây đối xứng |

|

Trở kháng tải thử, W |

75 |

120 |

|

Điện áp đỉnh cực đại (Vop), V |

1,5 |

1,9 |

|

Điện áp đỉnh cực tiểu (Vop), V |

0,75 |

1,0 |

|

Giá trị rung pha đỉnh – đỉnh cực đại tại cổng ra |

Tuân theo mục 3.3.1 của Tiêu chuẩn TCN 68-164: 1997 |

|

Suy hao của đôi dây này phải tuân theo luật Öf, và suy hao tại tần số 2048 kHz phải nằm trong dải từ 0 đến 6 dB (giá trị nhỏ nhất). Suy hao này có tính đến bất kỳ sự suy giảm nào xảy ra do sự có mặt của giá phân bố tín hiệu số giữa các thiết bị. Suy hao phản xạ tại 2048 kHz phải lớn hơn hoặc bằng 15 dB.

Chú ý: Lớp dẫn điện bên ngoài của cáp đồng trục và vỏ bọc của đôi dây đối xứng phải được nối đất tại cổng ra. Trong trường hợp cần thiết thì vỏ bọc này phải được nối đất cả tại cổng vào.

3.3 Chỉ tiêu kỹ thuật về yêu cầu bảo vệ quá áp

Cổng vào và cổng ra phải đảm bảo không bị hư hỏng khi thực hiện các phép đo kiểm sau: 10 xung cao áp chuẩn (1.2/50 ms) với biên độ cực đại U (5 xung âm và 5 xung dương).

n Tại giao diện cho cáp đồng trục:

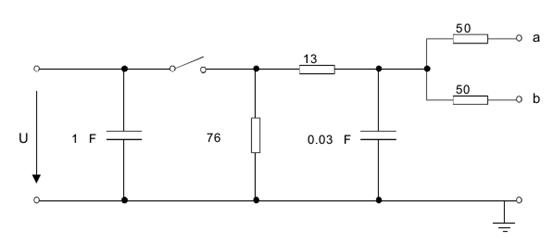

a) Chế độ điện áp chênh lệch: sử dụng bộ tạo xung quy định như trên hình 3.

b) Chế độ điện áp so với đất: đang được nghiên cứu.

Hình 2: Dạng xung tín hiệu đồng bộ 2048 kHz.

n Tại giao diện của đôi cáp đối xứng

a) Chế độ điện áp chênh lệch: Bộ tạo xung được quy định như trên hình 3,

Có thể lấy giá trị U = 20 V.

b) Chế độ điện áp so với đất: Với bộ tạo xung như trên hình 4, giá trị U = 100 V (Một chiều)

Hình 3: Bộ tạo xung chế độ điện áp chênh lệch 1,2/50 ms.

Hình 4: Bộ tạo xung 1,2/50 ms chế độ điện áp chung.

TÀI LIỆU THAM KHẢO

1. CCITT – Recommendation G.703

Physical/Electrical Characteristics of Hierarchical Digital Interfaces, Geneva 4-1991.

2. Tiêu chuẩn ngành TCN 68-164 : 1997

Lỗi bit và rung pha của các đường truyền dẫn số – Yêu cầu kỹ thuật và Quy trình đo kiểm.